Verilog Code For Serial Adder Subtractor 4

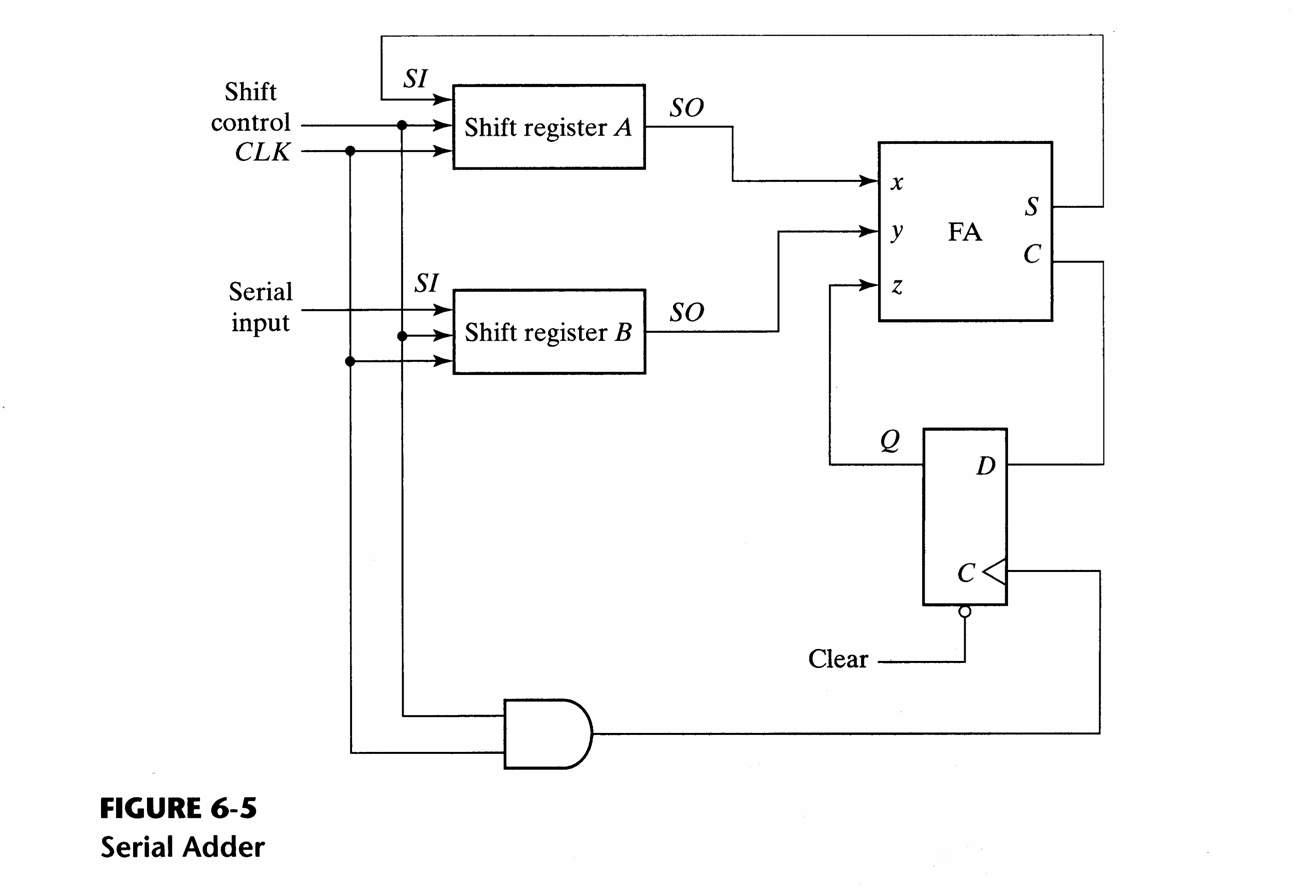

Jul 17, 2013 Design of 4 Bit Adder using 4 Full Adder Structural Modeling Style (Verilog Code) 03:58 Naresh Singh 3 comments Email This BlogThis! Design a serial adder circuit using Verilog. The circuit should add two 8-bit numbers, A and B. The result should be stored back into the A register. Use the diagram below to guide you. Hint: Write one module to describe the datapath and a second module to describe the control.

These design examples may only be used within Intel Corporation devices and remain the property of Intel. They are being provided on an “as-is” basis and as an accommodation; therefore, all warranties, representations, or guarantees of any kind (whether express, implied, or statutory) including, without limitation, warranties of merchantability, non-infringement, or fitness for a particular purpose, are specifically disclaimed. Intel expressly does not recommend, suggest, or require that these examples be used in combination with any other product not provided by Intel.

Due to recent changes by Oracle, java applets have become difficult to run in the browser. To mitigate the troubles, Oracle has provided the following websites to help users troubleshoot: and Even after following the above instructions, loading applets may still show warning concerning “unsigned application” and “unknown publisher”. For Teahlab in particular, these warnings are due to the fact that we have opted not to pay a third party such as Verisign to sign our applets. Any warning that comes up when you try to run our applets should emphasize that our applets will always run with “limited access”, which is Oracle’s way of letting you know that teahlab doesn’t do anything on your computer except running the circuits you see: in other words, our applets are safe to run. Sincerely, The Teahlab Team. Your browser does not support iframes.

Structure: -- -- This program is a structural VHDL design of the 4-bit -- Adder-Subtracter. By structural we mean that the -- circuit is constructed using XOR components and Full -- Adder components -- just like the actual physical -- Adder-Substractor. -- -- Consequently, this VHDL circuit is designed in two -- stages. In stage one we define the XOR entity and then -- the Full Adder entity. Here we present a dataflow -- design of the Full Adder circuit. For the structural -- (RTL) design of the circuit, see the Full Adder page -- on Teahlab.com. -- -- In stage two we build the structure of the -- Adder-Substractor using the components we build in -- stage one. Hacienda buena vista ponce telefonos.

-- -- It is very important to learn structural design (RTL) -- strategies because as your assignments become larger -- and larger, knowledge of register transfer level (RTL) -- design strategies become indispensable.